# IM29LV001T and IM29LV001B 1 M Bit (128K x 8) 3.3V-Only Flash Memory

#### Features:

- 0.40 µm, triple-poly double-metal CMOS process

- Single power supply operation

3.3V ± 10% for both read and write

- High endurance

> 10,000 program/erase cycles

Fast read access time

70 and 90 ns

Single page erasability for optimal data alterability

Page size: 512 bytes

Hardwired data protection

Inhibits program and erase operations of the top (IM29LV001T) or bottom (IM29LV001B) 32 pages of the array for false write and virus prevention.

- Flexible boot block configurability

- · Fast program and erase operations:

Byte program : < 35 µsec typical

Page erase : < 7 msec typical Chip erase : < 2 sec typical

- Self-timed program/erase operations with end-of-cycle detection

- Data# Polling and Toggle Bit

- Inadvertent write protection

Glitch filtering for WE# and CE#

Low Vcc (< 2.2 V ) write inhibit

Hardwired data protection

- Low lcc for power conservation

Read: 6 ma typical Write: 10 ma typical Stand-by: 10 µA typical

- Compatible with JEDEC byte wide pinout and single-supply flash command standards

- · Package types:

32-pin PLCC, TSOP and PDIP Others available upon request

# **General Descriptions**

The IM29LV001T/B is a 1 Mega-bit, 5V-only page erasable flash memory organized as 128K X 8 bits.It is manufactured with IMT's proprietary double metal, 0.40 µm CMOS flash technology. High performance cell design and advanced process technology attain better reliability, manufacturability, circuit performance and future scaleability than other alternative approaches. Fast, self-timed program/erase operations are made possible with an innovative cell and array architecture which is free from the over-erase problem of the traditional stacked-gate structures.

Single page (512 bytes) data alterability ensures optimum flexibility and efficiency in program codes, parameters and data storage. It also allows backward compatibility

to other large-erase-block based flash products for direct replacement.

The IM29LV001T/B is designed with interface features for direct in-system programming and erase operations. Vendor re-programmable, hardwired data protection is provided for absolute prevention in inadvertent data alteration and virus infection.

The IM29LV001 conforms to the JEDEC byte wide memory pin-out and single supply flash command standards.

Designed, manufactured and tested for extended endurance applications, the IM29LV001 is specified for more than 10<sup>4</sup> cycling endurance and greater than 10 years of data retention.

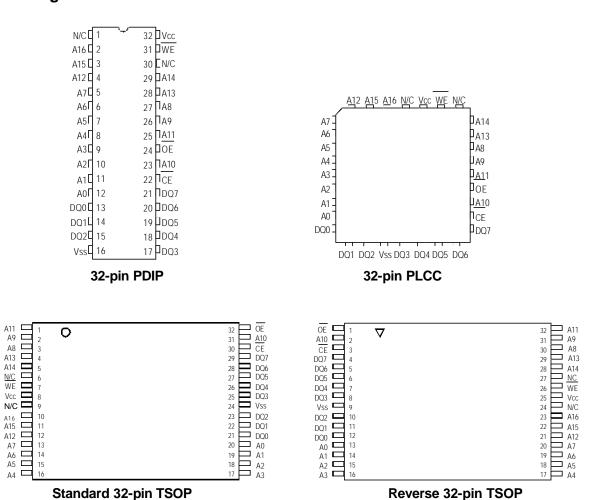

### **Pin-out Assignments**

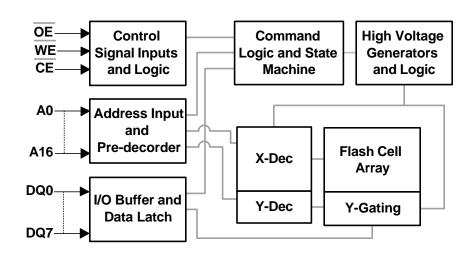

# **Block Diagram**

#### Flexible Boot Block Architecture

The page erase function of IM29LV001T/B erases only the bytes located inside the 512byte boundary (as defined by A9 - A16) of the selected page. It does not affect any other memory location outside of the page boundary. Any page of the array can be used as an independent data storage unit which is not affected by the erase and programming operations of the rest of the array. A boot block of any size can be constructed by selecting a contiguous, or non-contiguous if so desired, group of pages from the top or bottom address. This provides the most convenient boot block configuration than those utilizing the fixedsize boot block approach.

#### **Hard Wired Data Protection**

A hard wired data protection option is provided for the first 32 pages either from the top address (IM29LV001T) or from the bottom address (IM29LV001B). This option can be utilized to protect the BIOS boot codes which

usually reside in the top or bottom 16K-byte address range.

# **Device Operation**

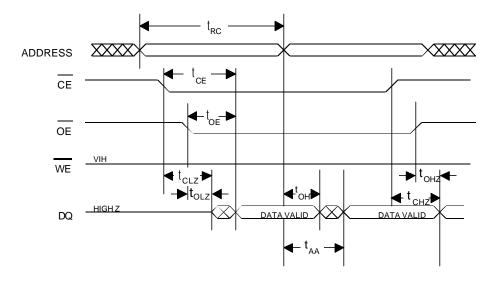

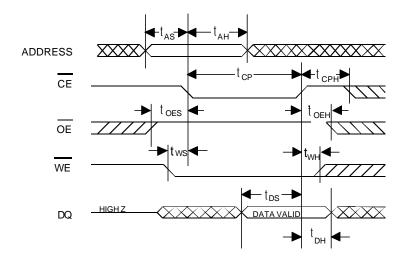

#### Read

The read operation of the IM29LV001T/B is activated by setting CE# and OE# to low  $(V_L)$  and WE# to high  $(V_H)$ . Data is obtained from the output pins. CE# controls the device selection function. When CE# is high, the device is deselected and only standby power is consumed. When CE# is low, the device is selected. OE# controls the output buffer. It is used to gate data from the output pins. The data bus is in high impedance state when

either CE# or OE# is high. See Fig. 1 for the read cycle timing diagram.

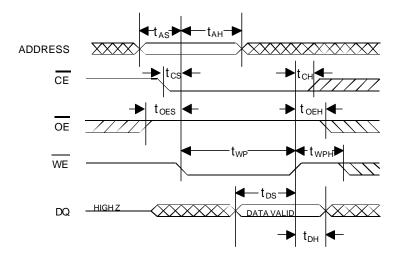

#### Write

The write operation is used to issue commands and data for the program and erase functions of the device. It is initiated by forcing CE# low, OE# high and WE# low. The addresses are latched by the falling edge of either CE# or WE#, whichever occurs last. The data is latched by the rising edge of either CE# or WE#, whichever occurs first. See Fig. 2 for the timing diagram of writing a command with WE# as the controlling signal, and Fig. 3 for that with CE# as the controlling signal.

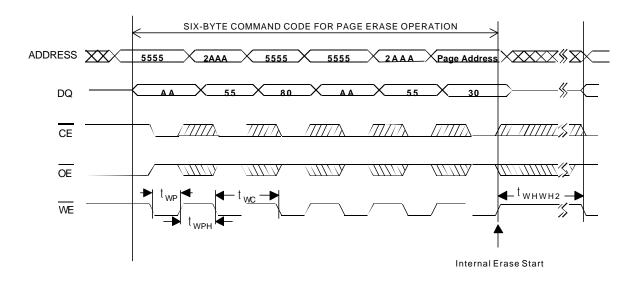

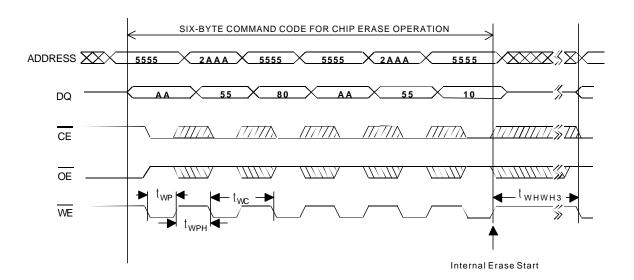

#### **Erase: Page and Chip Erase**

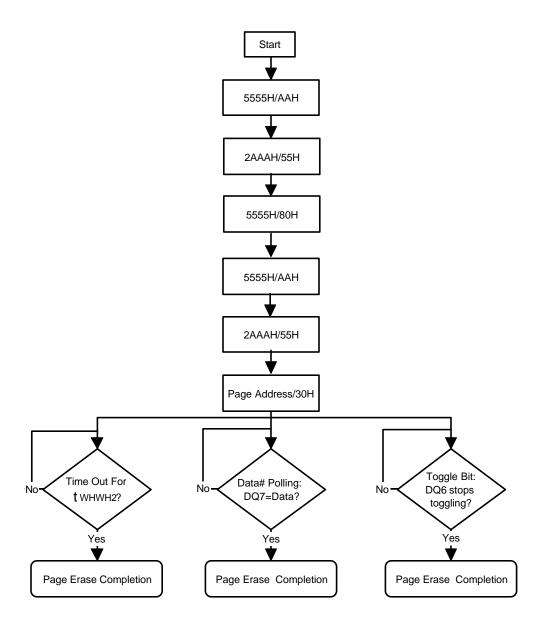

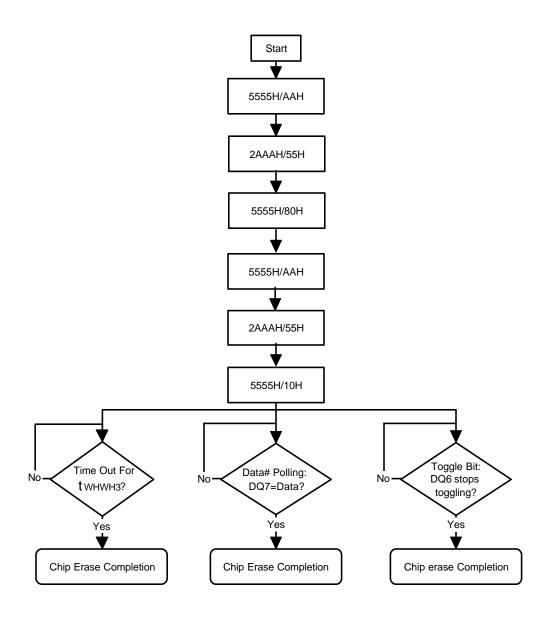

The IM29LV001T/B provides two erase functions: page erase and chip erase. The page erase function erases a single page (512 bytes in size) at a time. It is activated by writing the page erase command to the part. The page erase command is consisted of 6 write cycles as shown in Table 2. The first 5 cycles contain the command codes, while the 6<sup>th</sup> cycle asserts the page address (A9 to A16) by forcing the correct address signals to the address pins. See Fig. 9 for the flow chart and Fig. 5 for the page erase timing diagram. The chip erase function erases the complete 1 mega-bit array simultaneously. It is activated by a 6-byte command cycle shown in Table 2. See Fig. 6 for the timing diagram and Fig. 10 for the flow chart.

The page and chip erase operations, once initiated, will trigger an internal timer to start the erase operation until completion, which takes typically 6 ms for the page and 2 sec for the chip erase. During this period, the data and address buses of the part are in high impedance states. The system buses

| OPERATION                      | CE#             | OE#                   | WE#             | A0                     | A1                     | A9                     | I/O                       |

|--------------------------------|-----------------|-----------------------|-----------------|------------------------|------------------------|------------------------|---------------------------|

| Read                           | V <sub>IL</sub> | V <sub>IL</sub>       | V <sub>IH</sub> | A <sub>in</sub> Note 1 | A <sub>in</sub> Note 1 | A <sub>in</sub> Note 1 | D <sub>out</sub>          |

| Standby                        | V <sub>IH</sub> | Х                     | Х               | Х                      | Х                      | Х                      | HIGHZ                     |

| Output Disable                 | V <sub>IL</sub> | V <sub>IH</sub>       | V <sub>IH</sub> | Х                      | Х                      | Х                      | HIGHZ                     |

| Write                          | $V_{IL}$        | V <sub>IH</sub>       | V <sub>IL</sub> | A <sub>in</sub> Note 1 | A <sub>in</sub> Note 1 | A <sub>in</sub> Note 1 | D <sub>IN</sub>           |

| Enable Hardwired Data Protect  | V <sub>IL</sub> | V <sub>H</sub> Note 1 | V <sub>IL</sub> | Х                      | Х                      | V <sub>H</sub> Note 1  | Х                         |

| Disable Hardwired Data Protect | V <sub>H</sub>  | V <sub>H</sub> Note 1 | V <sub>IL</sub> | Х                      | Х                      | V <sub>H</sub> Note 1  | Х                         |

| Verify Hardwired Data Protect  | $V_{IL}$        | $V_{IL}$              | V <sub>IH</sub> | $V_{IL}$               | V <sub>IH</sub>        | V <sub>H</sub> Note 1  | CODE                      |

| Product Identification         |                 |                       |                 |                        |                        |                        |                           |

| Manufacturer ID Byte 1         | $V_{IL}$        | V <sub>IL</sub>       | V <sub>IH</sub> | V <sub>IL</sub>        | $V_{IL}$               | V <sub>H</sub> Note 1  | 7FH                       |

| Byte 2                         | $V_{IL}$        | V <sub>IL</sub>       | V <sub>IH</sub> | $V_{IH}$               | $V_{IH}$               | V <sub>H</sub> Note 1  | 1FH                       |

| Device ID                      | $V_{IL}$        | V <sub>IL</sub>       | V <sub>IH</sub> | V <sub>IH</sub>        | V <sub>IL</sub>        | V <sub>H</sub> Note 1  | A5H/A6H <sup>Note 2</sup> |

Note 1:  $V_H$ =12 V,  $A_{in}$  = address input, X = don't care. Note 2: A5H for IM29LV001T and A6H for IM29LV001B

**Table 1 Operation Modes**

are free for other operations.

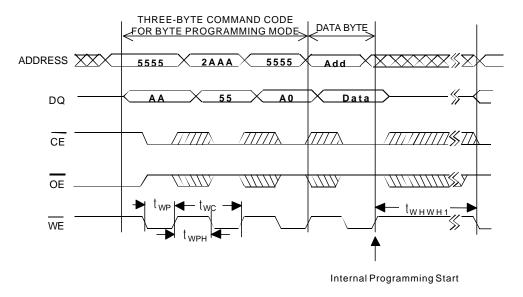

#### Program

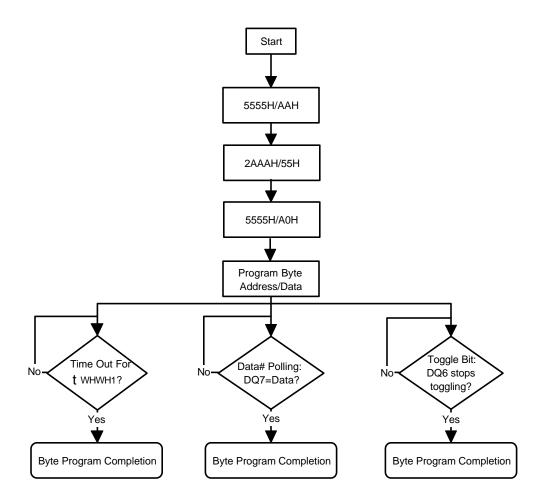

Byte program operation is initiated by issuing a program command which is consisted of 4 write cycles as shown in Table 2. The first 3 cycles contain the command codes and the 4th cycle asserts the byte address and data. See Fig. 11 for the flow chart and Fig. 4 for the timing diagram. The program operation, once initiated, will continue internally until completion, typically within 20 µs. During the byte programming period, the data and address buses of the part are in high impedance state. The system buses are free for other operations. For example, during the byte programming period, the host is free to perform other tasks, such as to fetch data from other locations in the system for the next byteprogram operation.

# Program/Erase Status Detection: Data# Polling and Toggle Bit

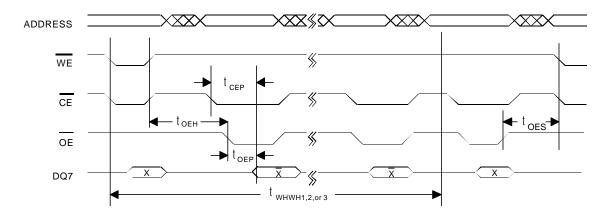

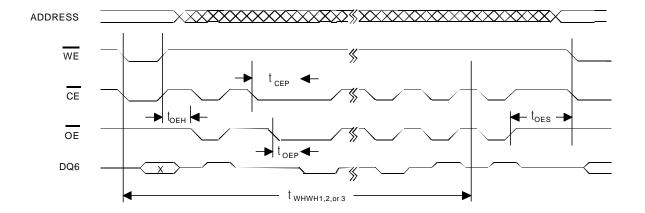

The IM29LV001T/B provides two status bits for detecting the completion of a program or erase period. They are the Data# Polling (DQ7) and Toggle (DQ6) bits. During the program or erase operation, the only valid read operations of the part are to read Data# Polling and Toggle Bits. Both bits are enabled and can be detected after the program or erase cycle is initiated by the first rising edge of WE# or CE# signal. See Fig. 7 and 8 for the timing diagrams and Fig. 9, 10 and 11 for the flow charts representation of the usage of Data# Polling and Toggle Bit in page erase, chip erase and byte program operations.

#### Data# Polling (DQ<sub>7</sub>)

When the IM29LV001T/B is in the program or erase period, any attempt to read  $DQ_7$  will receive the complement of the intended data of the program or erase operation. Once the program or erase cycle is completed,  $DQ_7$  will show true data. The device is then ready for the next operation. See Fig. 7 for Data# Polling timing diagram.

#### Toggle Bit (DQ<sub>6</sub>)

During the program or erase cycle, any consecutive attempts to read DQ<sub>6</sub> will produce alternating 0's and 1's. It will start with "0" and then toggle between "0" and "1". When the program or erase cycle is completed, the toggling action will stop. The device is then ready for the next operation. See Fig. 8 for Toggle Bit timing diagram.

#### **Data Protection**

The IM29LV001T/B provides both hardware and software features to protect nonvolatile data from inadvertent writes.

Optional Hardwired data protection for selected sectors: The program and erase operations of the first (IM29LV001T) or last (IM29LV001B) 32 pages can be disabled permanently to prevent false write and/or virus infection. As shown in Table 1, the hardwired protection mode can be enabled by applying V<sub>H</sub>, or 12 Volt, to A9 and OE#, and V<sub>II</sub> to CE# and WE#. The mode can be disabled by applying the same voltages to the above pins except CE#, where  $V_{\text{H}}$  is applied. To verify the status of the hardwired data protection mode, A9 is set to V<sub>H</sub> ( or 12 Volt), CE#, OE# and A0 to V<sub>L</sub>, and WE# and A1 to  $V_{IH}$ . If D0 = "1" then the hardwired data protection mode is enabled. Or vice versa, if D0 = "0". The status of the hardwired data

| Command                | First C | First Cycle Second Cycle |       | Third ( | Cycle | Four | th Cycle | Fifth Cycle             |       | Sixth Cycle |          |      |

|------------------------|---------|--------------------------|-------|---------|-------|------|----------|-------------------------|-------|-------------|----------|------|

|                        | Add     | Data                     | Add   | Data    | Add   | Data | Add      | Data                    | Add   | Data        | Add      | Data |

| Read                   | xxxxH   | F0H                      |       |         |       |      |          |                         |       |             |          |      |

| Reset/ Read            | 5555H   | AAH                      | 2AAAH | 55H     | 5555H | F0H  | Byte Add | Byte Data               |       |             |          |      |

| Program                | 5555H   | AAH                      | 2AAAH | 55H     | 5555H | A0H  | Byte Add | Byte Data               |       |             |          |      |

| Page Erase             | 5555H   | AAH                      | 2AAAH | 55H     | 5555H | 80H  | 5555H    | AAH                     | 2AAAH | 55H         | Page Add | 30H  |

| Chip Erase             | 5555H   | AAH                      | 2AAAH | 55H     | 5555H | 80H  | 5555H    | AAH                     | 2AAAH | 55H         | 5555H    | 10H  |

| Product Identification |         |                          |       |         |       |      |          |                         |       |             |          |      |

| Manufacturer ID        |         |                          |       |         |       |      |          |                         |       |             |          |      |

| Byte 1                 | 5555H   | AAH                      | 2AAAH | 55H     | 5555H | 90H  | xx00H    | 7FH                     |       |             |          |      |

| Byte 2                 | 5555H   | AAH                      | 2AAAH | 55H     | 5555H | 90H  | xx11H    | 1FH                     |       |             |          |      |

| Device ID              | 5555H   | AAH                      | 2AAAH | 55H     | 5555H | 90H  | xx01H    | A5H/A6H <sup>Note</sup> |       |             |          |      |

Note: A5H for IM29LV001T and A6H for IM29LV001B

**Table 2 Command Definitions**

#### **Preliminary Specification**

| Command               | First ( | Cycle | Second | Cycle | Third Cycle |      | Fourth Cycle |    |    |                                      |  |  |  |

|-----------------------|---------|-------|--------|-------|-------------|------|--------------|----|----|--------------------------------------|--|--|--|

|                       |         |       |        |       |             |      | Add          |    |    |                                      |  |  |  |

|                       | Add     | Data  | Add    | Data  | Add         | Data | A16 - A2     | A1 | Α0 | Data/Status                          |  |  |  |

| Read Hardwired        | 5555H   | AAH   | 2AAAH  | 55H   | 5555H       | 90H  | Don't Care   | 1  | 0  | Protected: D0 = 1, D7-1=Don't Care   |  |  |  |

| Protection Status Bit |         |       |        |       |             |      |              |    |    | Unprotected: D0 = 0, D7-1=Don't Care |  |  |  |

Table 3 Hardwired Protection Status Bit Read Command

protection mode can also be verified by software means. See Table 3 for the command code to access the status bit of the top and bottom sector. The hardwired data protection mode can not be disabled by software means, however.

Noise/Glitch Protection: A WE# or CE# noise glitch of less than 5 ns will not initiate a program or erase cycle.

$\underline{V_{CC}}$  Power Up/Down Detection: The program or erase operation is inhibited when  $V_{CC}$  is less than 3.5V.

<u>Write Inhibit Mode</u>: The program or erase operation is inhibited if any one of the following conditions is enforced: OE# low, CE# high, or WE# high. This prevents inadvertent data alterations during power-up or power-down period.

#### **Product Identification**

The product identification mode identifies the device as the IM29LV001T/B and the manufacturer as IMT. This mode may be accessed by hardware or software operations. They are typically used by a Flash Memory programmer to identify the IMT IM29LV001T/B device and apply the correct algorithm to program the data. See Table 1 for hardware operation or Table 2

for software operation codes. The manufacturer ID for IMT is consisted of two bytes. The first byte is 7F which is located at A0=0 and A1=0. The second byte is 1F, located at A0=1 and A1=1. The device ID is A1, located at A1=0 and A0=1. See Table 4

|                 |         |    | Byt | te 1                    | Byte 2  |       |      |      |  |  |

|-----------------|---------|----|-----|-------------------------|---------|-------|------|------|--|--|

|                 | Address |    | s   | Data                    | Address |       |      | Data |  |  |

| ID Type         | A16-2   | Α1 | Α0  |                         | A16-2   | Α1    | A0   |      |  |  |

| Manufacturer ID | Χ       | 0  | 0   | 7FH                     | Χ       | 1     | 1    | 1FH  |  |  |

| Device ID       | X       | 0  | 1   | A5H/A6H <sup>Note</sup> | Not A   | pplic | cabl | е    |  |  |

Note: A5H for IM29LV001T and A6H for IM29LV001B

Table 4 Product Identification Table

for manufacturer and device ID designations.

# Termination of Product Identification Mode

To return to the standard read mode, the Software Product Identification mode must be terminated. It is accomplished by issuing the Reset/Read operation, which returns the device to the read operation. See Table 2 for the Reset/Read command codes.

# **Absolute Maximum Ratings**

Storage temperature..... -65°C to +150 °C

Ambient temperature with power

applied.....-65°C to +125°C

Voltage with respect to ground

Vcc....-0.5 V to 3.6 V

A9 ....-0.5 V to +12.5 V

All the other pins... -0.5 V to Vcc + 0.5 V

# **Operating Ranges**

Ambient Temperature :

Commercial ( C ) Devices...0 °C to 70 °C

Industrial ( I ) Devices.....-40 °C to +85 °C

Extended ( E ) Devices....-55 °C to 125 °C

Vcc Supply Voltages: 3.0 V to 3.6 V

#### **DC Parameters:**

|                  |                                                                       | Limits |      |       |                                                                                  |

|------------------|-----------------------------------------------------------------------|--------|------|-------|----------------------------------------------------------------------------------|

| Symbol           | Parameter                                                             | Min    | Max  | Units | Test Conditions                                                                  |

| I <sub>cc</sub>  | Power Supply Current                                                  |        |      |       | CE#=OE#=V <sub>IL</sub> ,WE#=V <sub>IH</sub> , all I/Os open,                    |

|                  | Read                                                                  |        | 10   | mA    | Address input = $V_{IL}/V_{IH}$ , at f=1/ $T_{RC}$ , Min-, $V_{CC}=V_{CC}$ , Max |

|                  | Write                                                                 |        | 15   | mA    | $CE\#=WE\#=V_{IL}, OE\#=V_{IH}, V_{CC}=V_{CC}, Max.$                             |

|                  | Standby Power Supply Current                                          |        |      |       |                                                                                  |

| I <sub>SB1</sub> | TTL input                                                             |        | 1    | mA    | $CE\# = V_{IH}, V_{CC} = V_{CC}, Max$                                            |

| I <sub>SB2</sub> | CMOS input                                                            |        | 15   | μΑ    | $CE\# = V_{CC}$ -0.3V, $V_{CC} = V_{CC}$ , $Max$                                 |

| I <sub>L1</sub>  | Input Leakage Current                                                 |        | 1    | μΑ    | $V_{IN}$ =GND to $V_{CC}$ , $V_{CC}$ = $V_{CC}$ , $Max$                          |

| I <sub>LO</sub>  | Output Leakage Current                                                |        | 10   | μΑ    | $V_{OUT}$ =GND to $V_{CC}$ , $V_{CC} = V_{CC}$ , $Max$                           |

| V <sub>IL</sub>  | Input Low Voltage                                                     |        | 0.8  | V     | $V_{CC} = V_{CC}$ , Max.                                                         |

| $V_{IH}$         | Input High Voltage                                                    | 2.0    |      | V     | $V_{CC} = V_{CC}$ , Max.                                                         |

| $V_{OL}$         | Output Low Voltage                                                    |        | 0.4  | V     | $I_{OL} = 2.1 \text{ mA}, V_{CC} = V_{CC}, Min.$                                 |

| $V_{OH}$         | Output High Voltage                                                   | 2.4    |      | V     | $I_{OH} = -400 \mu A$ , $V_{CC} = V_{CC}$ , Min.                                 |

| V <sub>H</sub>   | High voltage input for Product ID and Hardwired Data Protection modes | 11.5   | 12.5 | V     | $CE\# = OE\# = V_{IL}, WE\# = V_{IH}$                                            |

| l <sub>Η</sub>   | High voltage input for Product ID and Hardwired Data Protection modes |        | 50   | μΑ    | $CE\# = OE\# = V_{IL}, WE\# = V_{IH}, A_9 = V_{H_1 Max}$                         |

#### **AC Parameters:**

# a) Read Characteristics:

| Parameter        | Description                     | IM29LV001-<br>55 |     | IM29LV001-<br>70 |     | IM29LV001-<br>90 |     | IM29LV001-<br>120 |     |      |

|------------------|---------------------------------|------------------|-----|------------------|-----|------------------|-----|-------------------|-----|------|

|                  |                                 | Min              | Max | Min              | Max | Min              | Max | Min               | Max | Unit |

| t <sub>RC</sub>  | Read cycle time                 | 55               |     | 70               |     | 90               |     | 120               |     | ns   |

| t <sub>AA</sub>  | Address to output delay         |                  | 55  |                  | 70  |                  | 90  |                   | 120 | ns   |

| t <sub>CE</sub>  | CE# to output delay             |                  | 55  |                  | 70  |                  | 90  |                   | 120 | ns   |

| t <sub>OE</sub>  | OE# to output delay             |                  | 25  |                  | 35  |                  | 45  |                   | 60  | ns   |

| t <sub>CLZ</sub> | CE# low to output active        | 0                |     | 0                |     | 0                |     | 0                 |     | ns   |

| t <sub>OLZ</sub> | OE# low to output active        | 0                |     | 0                |     | 0                |     | 0                 |     | ns   |

| t <sub>CHZ</sub> | CE# high to output at high-Z    |                  | 20  |                  | 30  |                  | 40  |                   | 50  | ns   |

| t <sub>OHZ</sub> | OE# high to output at high-Z    |                  | 20  |                  | 30  |                  | 40  |                   | 50  | ns   |

| t <sub>OH</sub>  | Output hold from address change | 0                |     | 0                |     | 0                |     | 0                 |     | ns   |

# b) Write Characteristics:

| Parameter          | Description                                              | IM29LV001-55 |     | IM29LV | 001-70 | IM29LV | 001-90 | IM29LV |     |      |

|--------------------|----------------------------------------------------------|--------------|-----|--------|--------|--------|--------|--------|-----|------|

|                    |                                                          | Min          | Max | Min    | Max    | Min    | Max    | Min    | Max | Unit |

| t <sub>WC</sub>    | Write command cycle time                                 | 55           |     | 70     |        | 90     |        | 120    |     | ns   |

| t <sub>AS</sub>    | Address setup time                                       | 0            |     | 0      |        | 0      |        | 0      |     | ns   |

| t <sub>AH</sub>    | Address hold time                                        | 35           |     | 45     |        | 55     |        | 60     |     | ns   |

| t <sub>DS</sub>    | Data setup time                                          | 20           |     | 30     |        | 40     |        | 45     |     | ns   |

| t <sub>DH</sub>    | Data hold time                                           | 0            |     | 0      |        | 0      |        | 0      |     | ns   |

| t <sub>OES</sub>   | OE# setup time                                           | 0            |     | 0      |        | 0      |        | 0      |     | ns   |

| t <sub>OEH</sub>   | OE# hold time                                            | 0            |     | 0      |        | 0      |        | 0      |     | ns   |

| t <sub>cs</sub>    | CE# setup time                                           | 0            |     | 0      |        | 0      |        | 0      |     | ns   |

| t <sub>CH</sub>    | CE# hold time                                            | 0            |     | 0      |        | 0      |        | 0      |     | ns   |

| t <sub>CP</sub>    | CE# write pulse width                                    | 25           |     | 35     |        | 45     |        | 50     |     | ns   |

| t <sub>CPH</sub>   | CE# write pulse width high                               | 20           |     | 30     |        | 30     |        | 35     |     | ns   |

| t <sub>ws</sub>    | WE# setup time                                           | 0            |     | 0      |        | 0      |        | 0      |     | ns   |

| t <sub>WH</sub>    | WE# hold time                                            | 0            |     | 0      |        | 0      |        | 0      |     | ns   |

| $t_{WP}$           | WE# write pulse width                                    | 25           |     | 35     |        | 45     |        | 50     |     | ns   |

| $t_{WPH}$          | WE# write pulse width high                               | 20           |     | 30     |        | 30     |        | 35     |     | ns   |

| t <sub>WHWH1</sub> | Byte programming time                                    |              | 30  |        | 30     |        | 30     |        | 30  | μs   |

| t <sub>whwh2</sub> | Page erase time                                          |              | 9   |        | 9      |        | 9      |        | 9   | ms   |

| t <sub>whwh3</sub> | Chip erase time                                          |              | 3   |        | 3      |        | 3      |        | 3   | s    |

| t <sub>CEP</sub>   | CE# access time for Data#<br>Polling and Toggle bit read |              | 55  |        | 70     |        | 90     |        | 120 | ns   |

| t <sub>OEP</sub>   | OE# access time for Data#<br>Polling and Toggle bit read |              | 25  |        | 35     |        | 45     |        | 60  | ns   |

#### **Test Conditions**

| Input rise and fall time           | 5 ns           |

|------------------------------------|----------------|

| Input pulse levels                 | 0.0 V to 3.0 V |

| Timing measurement reference level |                |

| Input                              | 1.5 V          |

| Output                             |                |

| Output loading                     |                |

| 55ns and 70 ns parts               |                |

| 90 ns and 120 ns parts             |                |

Fig. 1 Read Cycle Timing Diagram

Fig. 2 WE Controlled Command Write Timing Diagram

Fig. 3 CE Controlled Command Write Timing Diagram

Fig. 4 Byte Programming Mode Timing Diagram

Fig. 5 Page Erase Timing Diagram

Fig. 6 Chip Erase Timing Diagram

Fig. 7 Data Polling Timing Diagram

Fig. 8 Toggle Bit Timing Diagram

Fig. 9 Page Erase Flow Chart

Fig. 10 Chip Erase Flow Chart

Fig. 11 Byte Program Flow Chart